# Time Dilation, Technical Dilation, and Corporate Dilation

**TD Analysis Report**

Copyright © 2000 Michael D. O'Connor All Rights Reserved

### RELEASE NOTICE

This is the finished release document. Any previous document that does not bear this notice is a draft unreleased copy, and therefore is not the finished document. This document released 15 May 2000

# **Table of Contents**

| 1.0  | Executive Summary2 |                                                                           |     |  |  |

|------|--------------------|---------------------------------------------------------------------------|-----|--|--|

| 2.0  | Introduction       |                                                                           |     |  |  |

| 3.0  | Time Dila          | tion Defined and Redefined, and Defined Again                             | 7   |  |  |

| 4.0  | TD Anoma           | aly Probability Analysis                                                  | 10  |  |  |

|      | 4.1 Embe           | dded Systems                                                              | 14  |  |  |

| 5.0  | Technical          | Dilation                                                                  | 19  |  |  |

|      | 5.1 Critica        | al Treatise of Intel's Analysis of the Crouch-Echlin Effect Report        | 19  |  |  |

|      | 5.1.1              | Award 4.50g Versus C&T SCAT BIOS                                          | 19  |  |  |

|      | 5.1.2              | Automated Cycling Test Results                                            | 22  |  |  |

|      | 5.1.3              | Manual Cycling Test Results                                               | 23  |  |  |

|      | 5.1.4              | Glaring Intel Blunder                                                     | 29  |  |  |

|      | 5.2 A Bug          | in Intel's Whitney Chipset                                                | 59  |  |  |

|      | 5.3 Echlin         | 's TD Theory                                                              | 61  |  |  |

|      | 5.3.1              | Logic Path                                                                | 61  |  |  |

|      |                    | 5.3.1.1 Binary Coded Decimal Primer                                       | 67  |  |  |

|      | 5.3.2              | Introduction to RTC Data                                                  | 67  |  |  |

|      | 5.3.3              | RTC Data                                                                  | 71  |  |  |

|      |                    | 5.3.3.1 RTC Access Time Versus Software Reading Speed                     | 76  |  |  |

|      |                    | 5.3.3.2 RTC Access Time Versus Computer Speed                             | 78  |  |  |

|      |                    | 5.3.3.3 RTC Aggregate Access Time                                         | 80  |  |  |

|      |                    | 5.3.3.4 TD Test Lite Utility (TDTLELM.EXE) and TD Test Utility (TDTL.EXE) |     |  |  |

|      | 5.4 TD R           | elated Theoretical Causes Disproved                                       | 96  |  |  |

|      |                    | Miscellaneous                                                             |     |  |  |

|      | 5.5 DOS            | nterrupt 21 Set Date and Set Time Software Quirk                          | 105 |  |  |

| 6.0  | RTC Regi           | ster A Status Byte                                                        | 107 |  |  |

| 7.0  | Typical Co         | omputer Boot Process                                                      | 108 |  |  |

| 8.0  | Corporate          | Dilation                                                                  | 115 |  |  |

| 9.0  | Theoretica         | al Analysis and Conclusion                                                | 118 |  |  |

| 10.0 | Access Ti          | me Source Code                                                            | 125 |  |  |

|      | 10 1TIME           | VENT.ASM Source Code                                                      | 126 |  |  |

|     | 10.2BIOSACC.ASM Source Code                           | -131 |

|-----|-------------------------------------------------------|------|

|     | 10.3RTCACC.ASM Source Code                            | -132 |

| 11. | 0Web Sites                                            | -133 |

|     | 11.1Humorous Sites                                    | -133 |

|     | 11.2Microsoft Y2K Solution Product Links to Web Sites | -134 |

|     | 11.3Michael Kennedy's Web Site                        | -135 |

|     | 11.4Other Web Sites                                   | -136 |

# **Disclaimer**

The author of this report makes no guarantee as to the accuracy of this document, and does not provide any warranties or conditions, expressed or implied, including without limitation, any warranty of merchantability or fitness for a particular purpose. The author shall not be liable for any damages resulting from the use of this report or the data herein.

This report is written solely by the author without the auspices of any company or entity.

# **Distribution Policy**

Distribution of this report is authorized under the following conditions:

- 1. This report shall be distributed **free of charge** with nothing attached to it except as an attachment to email.

- 2. This report shall not be bundled, packaged, attached, or otherwise tied to or with any merchandise or product.

- 3. This report shall not be posted on web sites for display without prior consent of the author. The only exception to this are forums, BBS's, and FTP sites where this report may be posted as a downloadable item only.

- 4. This report shall not be distributed for profit, including distribution charges.

- 5. This report shall not be modified in any way, shape, or form, including the PDF file type of this document.

This report was generated using Microsoft® Word 97 and then converted into Acrobat PDF document using Adobe Acrobat<sup>™</sup> 4.0.

### Acknowledgements

First acknowledgement goes to Harlan Smith, whom I am very sorry to hear he has passed on before I had a chance to fulfill my promise to him that I will release this document soon.

Mr. Harlan Smith was the sole person responsible for getting this author into this mess regarding Time Dilation, as it was called at the time. Mr. Smith had strong reservations about the truth regarding TD - not from the author, but from the Crouch-Echlin group. This has remained true until the last day.

Second acknowledgement goes to Mr. Michael Kennedy, who in a span of one month kept the author's way of thinking in check with his own experience with BIOS chips and RTCs. He is a witness to the fact that Mr. Harlan Smith takes to the views of the author regarding TD, as well as those of Mr. Kennedy.

The acknowledgements also go to others who've worked with this author in the past, most of whom have passed on to other endeavors. Some of these were included in the semi-clandestine discussions via group email regarding the growing subject of the then-relatively-new discovery initially called Time Dilation (TD), which is now renamed "Time and Date Instabilities" but retaining the acronym "TD."

Regarding Mr. Harlan Smith, there had been differences regarding the effect of Y2K - Harlan on the seriousness of Y2K effect nationwide, even worldwide, and the author on how small the effect really is. The author still believes the effect will be localized rather than nationwide. It is agreed that the Y2K effects of most nations other than the USA are a serious threat to the USA counterparts, but the USA has the technology and expertise for remedial actions to correct the Y2K issues. The question, of course, is whether the available resources are sufficient.\* This author helped him to see that the GPS satellites are not as subject to weather-induced Y2K problems as he initially feared (I am an engineer involved in satellite communications).

The author first predicted in 1997 that the Y2K issue would become a political issue. It did, but it is still not on any candidate's platform in the year 2000 presidential elections.

This report is released in Harlan Smith's memory. It is a good report ©

It is now obvious that the Y2K scare has mostly fizzled out at the time of this release.

# 1.0 Executive Summary

Time Dilation (TD) is a rare computer anomaly defined as an excessively advanced or retrogressed system time or date relative to the actual time or date. It is observable after a computer is turned on and booted. The anomaly can occur on PC systems from 286 to 486, and in some cases may occur on certain non-PCI Pentiums (Pentium Overdrives on 486 motherboards). According to the prevailing theory, the anomaly is more likely to occur on older systems than new ones, because processor speed generally affects anomaly occurrence across computer platforms,\* and because some older BIOS firmware are not fully RTC-compliant.

This report shows conclusively that the TD anomaly is actually an "old" problem in terms of existence on computer platforms. The older the platform is today, the more prevalent the problem may be. In contrast, the newer the computer, the less probability the occurrence of the TD anomaly. In fact, there are indications that today's computers have already started to evolved away from the TD anomaly.

This report theorizes that the anomalies appear on these computer platforms if the BIOS code is not RTC compliant. Real Time Clock (RTC) chips with double-buffered registers never has exhibited a TD anomaly. New computers today may still have non-buffered RTC chips, but some have buffered RTC chips installed. The question, then, is which computer manufacturer installs buffered RTC chips? The question should be asked to a computer vendor before buying a computer.

This report does not discredit Time Dilation itself as a concept. It indeed exists, but it no more exists on computers than Windows 3.1 still exists on some computers, or no more than 386-based computers are still being used in small companies.

With this report, to bring the matter to a close is the ultimate purpose. While the *cause* of Time Dilation anomaly has never been proven by any corporation, person, or entity, this report does examine a singular, likely cause. It also examines and disproves certain claims and theories as to the cause of the TD anomaly.

2

<sup>\*</sup> Although processor speed affects the RTC access time, the access time is not a primary factor for the TD anomaly occurrence. The update period occurs once per second, and the slower the processor speed, the longer the access time, thus increasing the odds of TD anomaly occurrence.

There are technical blunders in technical papers as well as incorrect, untenable, or impractical technical theories submitted by some parties. This report examines almost exclusively publicly available technical reports and theories written by Intel and Crouch/Echlin group.

In summary, this report concludes that:

- 1. The TD anomaly has only one symptom: an excessively advanced or retrogressed system time or date relative to the true time or date.

- 2. An advanced time or date anomaly is hard to disprove, while a retrogressed time or date anomaly may be hard to prove. There is no scenario or condition identified with causing a false case of retrogressed time/date anomaly that <u>also</u> causes a false case of advanced time/date anomaly.

- 3. Test data in Intel's public report, Analysis of the Crouch-Echlin Effect, shows strong evidence of advanced time anomaly in addition to the BIOS time conversion anomaly, which conversion anomaly is presented in their report in terms of a theory instead of using test data to support it. The advanced time anomaly is not covered in their report.

- 4. Echlin's "Logic Path" theory is conclusively disproved because the date conversion routine is performed after the date is retrieved from the RTC, not while the date is in the process of being retrieved.

- 5. Echlin's diagnostic utilities, including RTC.EXE (discontinued in late 1998), are conclusively shown to return erroneous timing information in the returned results on 286 computers because they run too slowly on these computers (mainly due to machine speed and the programming language used). This impacts 286 computers allegedly found susceptible to the TD anomaly, but actually may not have it.

- The RTC chip itself is conclusively cleared as the culprit for the TD anomaly, because its time and date information is always correct.

- 7. During computer boot, the time and date information is separately processed: the time during POST, and the date after POST. Echlin/Crouch group suggests (on their web pages) both are processed together.

- 8. By theoretical analysis, the BIOS firmware code is the culprit for the TD anomaly, but there are many different versions of the code. Much depends on the integrity of the BIOS code. Not all BIOS code are suspect, however, because even in 1985 some BIOS code are robust.

This report covers three major areas: Time Dilation, because it is a misnomer as an accurate name for the anomaly, but nevertheless is more accurate than "Time and Date Instabilities" which implies more than one symptom; Technical Dilation, because there are flaws in technical presentations on both sides of this issue; Corporate Dilation, because some corporations are not meeting the evidence of the TD anomaly squarely in the face.

Some corporations who initially confirmed the TD anomaly have about-faced their foot-shifting stance on the anomaly because of alleged lawsuit fears from this TD "fallout," even when faced with the evidence. Other companies have thoroughly investigated the TD anomaly but without so much as even a single TD anomaly symptom, and the anomaly is chalked up as mere "hype and hysteria." Still others jumped on the bandwagon and sought to monopolize the fanned fears of this anomaly by providing the same software and/or hardware fixes offered for Y2K remediation.

Public exposure of this anomaly through web sites, some newspaper reports, and word-of-mouth eventually resulted in major corporations getting involved by testing for this anomaly. One U.S. corporation had found the presence on one computer and publicly confirmed it by means of newsgroup email, but eventually reversed itself after another U.S. corporation acquired it.

There are known bugs and conditions which are known to exhibit retrogressed time/date symptoms, but is a false TD anomaly. Verification of a retrogressed time or date symptom as a true TD anomaly requires a measure of technical knowledge on how the time and date information is processed in a computer boot. This is unfortunate but true.

However, reports of a TD anomaly showing an *advanced* time or date symptom is a much stronger indication of a true TD anomaly, especially an *excessive* advanced time/date symptom. There is no precedent for this symptom because there is no known bug or condition that causes it.\*

<sup>\*</sup> The time/date RTC initialization limitation is the only exception (known since at least 1987) that causes a one-day advance in the date, but this anomaly occurs only when *setting*, not reading, the RTC time/date 1 second before midnight on the last day of the month. This anomaly is revealed in the Hitachi technical data sheet for the Japanese version HD14681A RTC chip, and is *not* present in Motorola technical data sheet.

As far as the world knows, there is only one computer exhibiting an advanced date anomaly, and that is Mr. Jace Crouch's affectionately named "Zoom" 286 computer. However, this report reveals proof of advanced time anomaly on another machine – Mike Echlin's Zenith 286 board, which Intel tested. Intel claims the TD anomaly on this board was not found, but an advanced time anomaly on this computer cannot be denied or disproved in this report.

Yes, there were reports of other computers exhibiting TD anomaly, but accurate description of the anomaly itself (even to identify whether it is *advanced* or *retrogressed*) is sorely lacking. While the Crouch/Echlin group has changed the definition of TD at most three times since its conception, the general public and corporations still have no clear understanding of this definition to help them properly diagnose a TD anomaly. As a result, individual reports of the TD anomaly tend to be questionable if a detailed description of the observed anomaly is not included. The lack of proper definition of the TD anomaly itself tends to lead to false reports by people who do not understand it.

As far as embedded systems go, the TD anomaly may be more prevalent because 286 processors are used. However, its prevalence depends on a number of factors, including the presence of RTC chips, the system BIOS in use, whether system boots are regularly performed, and whether embedded systems are used in industries or in consumer products.

In conclusion, the TD anomaly is rare and will be even rarer as time goes on. TD is real enough, but not big enough.

### 2.0 Introduction

This document is intended to put to rest public apprehensions of a "fallout" from a computer anomaly first known as "Time Dilation" (TD), now renamed "Time and Date Instabilities" but retaining the acronym "TD." It is also called the "Crouch-Echlin Effect."

Randall Bart first coined the term "Time Dilation" at the time of the discovery. In Einsteinian physics, it refers to the phenomenon where an observer moving at high speed or in a strong gravity experiences time at a different rate than another observer in another frame of reference. At the time of the discovery, it was a reference to the RTC chip that is "experiencing time" at a different rate than our perception of time. However, the term is not an accurate representation of the anomaly, therefore it was renamed "Time and Date Instabilities" by Mr. Jace Crouch.

This document will show the following:

- Why TD anomaly has one symptom and one cause only

- Strong evidence of TD anomaly in Intel's test data in their report

- Mike Echlin's "Logic Path" theory debunked

- The difference between advanced and retrogressed time/date anomalies

- Real Time Clock (RTC) not the culprit for TD anomaly

- The importance of speed in reading RTC data on slow computers

- Characteristics of TD points to rare occurrence

- Most causative theories of TD debunked

- Typical computer boot process

- TD anomaly theory and culprit

# 3.0 Time Dilation Defined and Redefined, and Defined Again

On the web site hosted by Mr. Crouch is a 4-page document detailing Echlin's hypothetical theory of the TD anomaly. An excerpt states:

Certainly there are other causative factors behind the various time and date instabilities that are commonly known as the Crouch-Echlin Effect, including known BIOS problems, incompatible add-in cards or device drivers, and just plain old sloppy BIOS code. As Mike Echlin told me earlier this year, "what we have found is not a single problem, but a multitude of closely related problems that show similar symptoms." 1

Except for "sloppy BIOS code," the "causative factors" listed are not necessarily the cause of the anomaly; indeed, the cause has not even been found, much less conclusively proven, even though the anomaly have been "observed" by some Digital and Compaq employees. (They saw the mouse, but never saw its parents or the hole in the wall.\*) The noted phrase in the above excerpt is "similar symptoms," which is in the plural sense. Only one symptom identifies the TD anomaly: an excessively advanced or retrogressed date or time. In fact, the investigation started out that way. The obvious attempt is to hoard up "other causative factors" as multiple causes for TD, which was not the case during the author's tenure. The fact at the time was that a process of elimination was used in an attempt to find the culprit.

The "multitude of closely related problems that show similar symptoms" – although not named – is likely not directly related to the TD anomaly. Note that the narrative calls it "closely related problems" – plural sense – and not specifically a TD anomaly. The phrase "similar symptoms" also indicates this. The narrative did not further elaborate on what these are. Neither did the narrative point out what is *not* the cause of the TD anomaly. They are:

- Dead or weak battery

- Cold solder joint

- Unsynchronized DOS time with RTC time<sup>†</sup>

- Known DOS midnight rollover bug

- Known time/date RTC initialization limitation

- BIOS interrupt 1Ah routines

-

<sup>\*</sup> See end of Section 8.0.

<sup>&</sup>lt;sup>†</sup> Normally not exceeding a difference of a few seconds per day or less

Except the last item above, any of the rest will result in a *similar* symptom (note, singular) pointing to a TD anomaly, but none of them are the *cause* of the anomaly. There is only one TD anomaly symptom: a substantial change in system time/date information forward or backward relative to the true date/time. This symptom is observable by examining the system date and time on a computer after a computer boot. A TD anomaly occurs only *during* a computer boot. The fact that it occurs only during a computer boot points to a *singular cause*, *because the same number of the same processes occur in the same sequence in every computer power-up*.\*

This singular cause is the BIOS code that, during computer boot, does not properly avoid the small segment of time occurring every second, in which the Real Time Clock (RTC) is updating itself with the date and time. Two other causes are system interrupts not disabled and missing I/O delay instructions. But ignoring the UIP bit is the only cause that result in bad data being read from the RTC.<sup>†</sup>

But a cause of TD anomaly can be falsely identified by a misdiagnosed symptom. An example of this is a dying battery in the computer. There are other cases of similar symptoms that have nothing to do with TD. If there is a way to properly diagnose a TD anomaly, it is this: if the system date or time shows an *advanced* date or time relative to the true date or time, it is proof positive of a TD anomaly. On the other hand, if the system date or time has *retrogressed* instead of advanced, it is not proof of a TD anomaly because any number of causes apply which have nothing to do with TD. Hence, for a retrogressed date or time symptom, further investigation is warranted. Even so, it is more likely to be non-TD related.

The TD definition has changed or expanded at most three times since the discovery. The current definition, as defined by the Crouch-Echlin group, now includes *multiple* causes and symptoms of the anomaly, but without specifying what these are. But these causes, identified in this report, were well known before the discovery. These invariably result in retrogressed time/date information, but can never result in *advanced* time/date information. For this reason, these extraneous causes (referred to as "causative factors" on Jace Crouch's web site) are not true causes of the TD anomaly. By analysis and process of elimination, a singular cause of the TD anomaly remains the single and only cause.

<sup>\*</sup> Of course, the boot process is different between a cold-boot and warm-boot.

<sup>&</sup>lt;sup>†</sup> The RTC access time does *not* exceed the 244-microsecond limit, as this report will show later. This is an attribute on which the "Logic Path" theory depends, which is conclusively disproved in this report.

Based on detailed analysis in this report, the culprit appears very likely to be bad BIOS code that does not honor the Update-In-Progress bit (UIP) in status register A of the RTC. This has not been proven conclusively by any person, company, or entity, but it is the most logical culprit since it is already known that the BIOS code in *some* BIOS chips does not honor the UIP. However, computer speed is a factor that determines whether TD shows up in a computer, as will be explained later in this report.

Echlin's TDFIX was initially released without a full understanding of the underlying cause for the TD anomaly, nor, for that matter, a full understanding of RTC design parameters and operation. In fact, both TDTEST.EXE and TDFIX.EXE utilities left interrupts enabled, which may cause the wrong address to be pointed to, thus producing invalid results. Leaving interrupts enabled during access to the RTC could cause the RTC port address index to be changed by another interrupt (because system interrupts are enabled).<sup>2</sup>

Both TDTEST and TDFIX utilities have been fixed in a subsequent release, which turns off the interrupts during RTC access. However, Intel did not test the new versions.<sup>3</sup>

According to Intel, Intel ran the TDFIX utility (initial version), which reported that "it found the Crouch-Echlin Effect symptom" not just on Echlin's Zenith computer, but on other computers. <sup>4</sup> The discrepancy detected was the time differences between the RTC and BIOS data area in memory. In fact, Intel by implication calls "discrepancies between RTC data and BIOS data" the "Crouch-Echlin symptom." <sup>5</sup> How much this difference in time was is not revealed. Intel did not elaborate.\*

The time difference in the RTC and BIOS data area is not the culprit for the TD anomaly, but *may* be a *symptom* of it. It is normal, however, for the time difference to be two seconds or so apart after a boot-up. It is also normal for this difference to widen slightly the longer the computer remains powered on, and this difference should be no more than a few seconds per day at the most. This normal characteristic is *not a case* of a TD anomaly.

Echlin's TDFIX provides a fix for the anomaly because the *problem* in itself, though not the *cause*, is well understood. What is not revealed is that this problem is not *widespread* as you may be led to believe. This is expounded later in this report.

<sup>\*</sup> Intel did elaborate in Appendix A of its report, but their elaboration is only a cleverly concocted *theory* that bears some elements of truth, but also hides another truth. See Section 5.1.4 in this report.

Finally, the TD anomaly is *not* related to Y2K problems because:

- 1. Y2K issues deal solely with the 2-digit year date problem, a known problem for which there is a known solution.

- 2. The TD anomaly is not caused by the fact that the century byte has to be included in the calculations after Y2K; it is caused by poor BIOS code that does not honor the UIP.

# 4.0 TD Anomaly Probability Analysis

In Jace Crouch's web page, three "map of a second" figures are shown.<sup>6</sup> While the maps are correct in terms of sequence (A, B, C, & D), some areas are overlooked which may contribute to some exaggeration of the truth. That the figures are not to scale contributes to a part of this exaggeration.

One such exaggeration is the misleading statement that *both* "time and date calculations" are made in a single process, thus leading the reader to believe that both time and date are retrieved from the RTC in the same process. In truth, the time information is retrieved from the RTC during POST, and the date information is retrieved *later*, after POST concludes. This means the RTC is accessed *twice*, once for the time, and again for the date, at two different times during computer boot.

Another misleading statement applies only to the date retrieval. In a typical 286 computer, *no calculation is performed* while the date is retrieved from the RTC. The calculation is performed by the DOS kernel *after* the date is retrieved from the RTC. The DOS kernel calls BIOS interrupt 1Ah to get the date from the RTC, and the BIOS code contains no such conversion routine to make the calculation.\*

<sup>\*</sup> See Section 5.3.1.

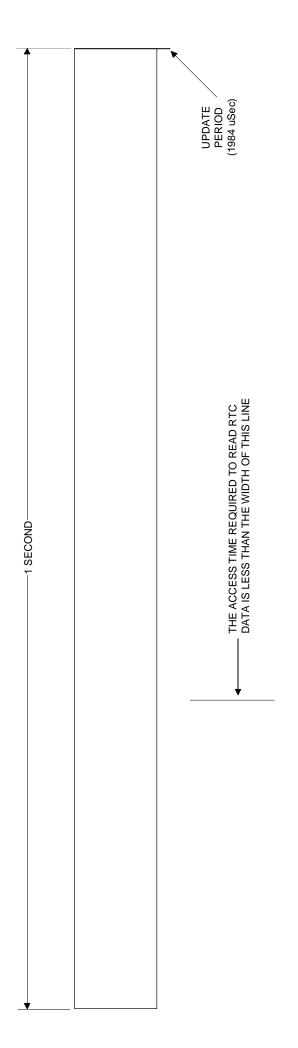

Figure 1 in this report shows an update in progress map scaled in size to the length of 10 inches (representing one second). For the purpose of this discussion, assume the access time required to obtain date/time information from the RTC is no more than 200 microseconds (0.0002 second). The documented update period which contains bad data is 1984 microseconds (0.001984 second).† The RTC is updated once per second to increment the seconds of time within the RTC in this period. The update period is represented in Figure 1 as a very thin line (actually a box) at the end of the one-second period. This line in the figure is extended beyond (below) the one-second "box" to show the size relationship with the one-second period.

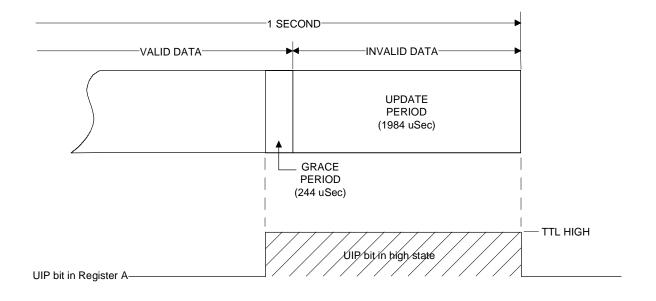

An expanded view of the update period is shown in Figure 2. The 244-microsecond window begins when the UIP bit is set active high. The update period begins after 244 microsecond window ends. Since the update period is 1984  $\mu$ s long, valid data is available in the entire remainder of the one-second period, or 0.998016 second, or 998,016 microseconds, or rounded to 998 milliseconds. The truth is that the 200-microsecond RTC access time can occur anywhere in this valid data period. There are 4,990 200-microsecond slots in this valid data period. In contrast, there are almost 10 200-microsecond slots in the update period.

Hence, there is a 1:500 chance (or 1:5000 chance, ignoring the 10 time slots in the update period) that RTC access will hit the update period, barring all other considerations.<sup>‡</sup>

This probability analysis only scratches the surface, because considerations make the odds of hitting the update period even smaller. These are:

- Computer speed (greater speed means shorter access time)

- Number of boots per year versus 1:500

- BIOS compliant to RTC specifications

- Different BIOS code and versions

- Improved RTC design (buffered registers)

- Newer computers

- Older computers with PCI bus architecture

- Any computer using OS/2 operating system

- Any computer using UNIX operating system

- Any computer using Microsoft Windows NT operating system

<sup>&</sup>lt;sup>†</sup> Motorola's Technical Data on RTC part number MC146818 and on Japanese version (Hitachi) part number HD146818

<sup>&</sup>lt;sup>‡</sup> The RTC technical data sheet statements regarding statistical numbers for random accesses, such as 1:4032 and 1:2032, are meaningless without more data to corroborate them. They appear to be based on factors other than presented here.

OS/2, UNIX, and Microsoft Windows NT operating systems do not use the BIOS to obtain the date from the RTC, either at boot time or during normal operation. They access the RTC directly. Therefore computers running these operating systems are not subject to the TD anomaly.

This analysis is based on an assumed access time (200 microseconds, aggregate). Faster computers mean less access time to retrieve RTC data. Therefore, the greater the computer speed, the shorter the access time, and hence the smaller the odds of the access time hitting the update period.

Intel reports that the RTC on Echlin's 286 12 MHz computer, which they tested, has the access time of 35 microseconds. This access time is the amount of time it takes to obtain 1 byte of data from the RTC. Retrieving the date takes 4 bytes, which amounts to an aggregate access time of 140 microseconds, which is a far cry from the 244-microsecond window. Therefore, on a 286 computer, there are 7,129 140-microsecond slots in the period in which data is valid. The odds of hitting the update period becomes smaller (1:700).

Regardless of the computer speed, if the BIOS routines consistently honor the UIP, no TD anomaly should occur, even if the RTC registers are not buffered, theoretically speaking.

If the RTC registers are 100% buffered (including during update period), no TD anomaly should occur, theoretically. This has been empirically shown in software testing by the Crouch/Echlin group. There is no reason to doubt it.

If the computer does show signs of the TD anomaly, it means the RTC has non-buffered registers and may mean the BIOS code does not consistently honor the UIP. What are the chances of this on a computer? It is much smaller than the 1:700 odds. The odds are also greatly reduced on faster computers. There are different computers with different speeds using different BIOS chips with different firmware, and the RTC registers may or may not be of buffered type. The odds are incalculable because there are too many varying factors involved.

There is no standard, method, recommendation, or routine in which BIOS routines should be written in all BIOS chips of all manufacturers. They are all different, because of different chipsets, motherboards, CPU chips, and RTC chips in use.

<sup>\*</sup> See Section 5.3.3.3.

Mr. Mike Echlin gave an account of test results on 100 PCs in an ICQ session with Mr. Harlan Smith in mid-January 1998. This test consists of a two-week manual test by using the computer normally, turning the computer off and on as normally would be done on a routine day, but with the date set to year 2000. Every time a computer is booted, the system time and date is manually recorded. The results below show a trend that the TD anomaly statistically occurs on more older computers than new ones.

| <u>Type</u> | TD?   |                                        |

|-------------|-------|----------------------------------------|

| 286         | 75%   |                                        |

| 386SX       | >75%  |                                        |

| 386DX       | 33%   | (I have checked mostly newer machines) |

| 486         | 25%~  | (33 Mhz and lower)                     |

| 486         | 12.5% | (Faster than 33 MHz)                   |

| 586         | 50%   | (Only on overdrives, only checked 4)   |

|             |       |                                        |

The last entry, it should be noted, consists of only four computers. The statements in parenthesis are Mr. Mike Echlin's clarifying notes. It should be noted that the "TD?" in the table header indicates that a TD anomaly has occurred, but has not been verified conclusively. There is no indication of advanced versus retrogressed anomaly; therefore, it only shows general problems which are undefined.

Most people, and especially companies in general, use newer computers to take advantage of better operating systems and applications. Hence the TD anomaly is almost certainly not a concern, but this is only one "plus" in this analysis. You will see henceforth that the very characteristics of the TD anomaly are series of "plusses" that work against its prevalence nationwide, even worldwide.

There is yet one more factor which greatly affects this probability analysis. It is the fact that, should a TD anomaly occur, the erroneous time or date information will be found in the BIOS data area (BDA), but the RTC date and time information *remains correct.* This being the case, a computer reboot will correct the problem. Hence, it is possible that a TD anomaly may pass by unnoticed by the user.\*

<sup>\*</sup> Assuming date-sensitive software is not loaded or is not affected by the date change.

However, the incorrect time or date in the BDA may be written to the RTC CMOS memory if the user sets the time or date with the DOS command TIME or DATE, or if a running program executes DOS Interrupt 21h function 2B (set date) or function 2D (set time). There is a software quirk in both Interrupt 21h functions: setting the date also sets the time in the RTC, and setting the time also sets the date. For example, setting the time of day will transfer not just the specified time of day, but also the incorrect date from the BDA to the RTC. See Section 5.5 for a description of this quirk.

# 4.1 Embedded Systems

One major area heretofore untouched in this analysis is embedded systems used in industries for such applications as automated systems and robotic manufacturing systems. Embedded systems still use 286-based microprocessors, which mean slower processing speed. If these embedded systems operate based on dates, the RTC would be needed. If not, there will never be a serious manufacturing problem due to a TD issue, whether an RTC is used or not.

But if so, there remains a determination whether time/date information is utilized in the system as part of the automated process. If so, then a further determination is needed as to whether the RTC uses non-buffered registers and whether the BIOS firmware does not honor the UIP. If so, then the chances of a TD anomaly will increase, but only in boot-ups. Remember that the TD anomaly depends entirely on system boot-ups. It does not manifest itself while the computer is running.\*

If such an embedded system exhibits a TD anomaly, replacement of the non-buffered RTC with a double-buffered RTC alone may not be a *complete* solution. The BIOS may also be replaced along with the RTC to take advantage of the buffered registers. This is especially true if provision to freeze the user copy of RTC buffers is included in the new RTC.

RTC/CMOS and I/O devices may be embedded in VLSI chips on some motherboards. If this is the case, the only solution is to replace the motherboard or replace the chip or chips containing the RTC and BIOS. Discrete chip replacement will require soldering skills and special equipment. This is also true for PCs.

<sup>\*</sup> Michael Kennedy's work on BCD-to-BIN theoretical experiment (see Section 11.3 for his web site URL) does not apply here. He specifically states that the data input to the test software does not come from the RTC or the BIOS.

An easier solution, therefore, is to replace the whole board with those chips installed. In fact, this is the best solution. For PCs, the simplest and effective solution is to install an adapter card with a buffered RTC and accompanying BIOS chip. Another solution is to purchase a new computer.

There are BIOS chips, even old ones (as early as 1985), which honor the UIP. Does the BIOS routine consistently honor the UIP? If yes, then a TD anomaly should theoretically never occur, buffered RTC or non-buffered RTC. Unfortunately, this question is not easy to answer with diagnostic software, even with Echlin's free TDTLELM.EXE diagnostic utility.\* This is because the BIOS firmware is different among different BIOS manufacturers.

Notwithstanding all this discussion regarding embedded systems, Mr. Patrick Bossert's† position is that the TD anomaly has no effect on embedded systems – those used in industries and plants. This is evident in a newsgroup post (uk.tech.y2k) dated sometime in April 1999. With the subject line "Time Dilation: does it effect Embedded Systems?" he has this to say:

...I prefer having a ringside seat on the PC issue, but I'm comfortable arguing my bit for embedded systems.

The answer is no it does not.

See <a href="http://www.embedded-science.com/faq/3.html">http://www.embedded-science.com/faq/3.html</a> for my dialogue with Mike Echlin on the subject... and arguments for why it doesn't.

But access into the above URL containing this "dialogue" requires a password. To get a password, you must go to the main page, click on the link to request access, and answer the required questions, including a commentary section.

However, a <a href="http://www.y2k-status.org/Embedded/PatrickMikeDialog.htm">http://www.y2k-status.org/Embedded/PatrickMikeDialog.htm</a> web page is open for viewing this "dialogue" referred to. Embedded systems are mentioned in the discussion. Based on the appearance and structure, the dialogue was probably conducted through email.

See Section 5.3.3.4.

<sup>&</sup>lt;sup>†</sup> Mr. Patrick Bossert is the inventor of a diagnostic device called the Delta-T Probe that performs extensive, technical analysis on RAM, ROM, and RTC chips used in embedded systems. It identifies the time and date information within an embedded system and captures the relevant code to allow the method of time and date comparison being used by the system to be examined in order to determine embedded system compliance.

In this dialogue, Mr. Patrick Bossert states that he has never observed a symptom of the TD anomaly on embedded systems. Further, according to Bossert, date windowing code is used *after* all the RTC date data has been read. This means "bounds checking" is employed to ensure the century year information fits within a particular range. But this does not mean TD will not occur within the date window.

Windowing is a method used to determine the century year (two high-order digits of the year) for a two-digit year by presupposing that the year falls in a specified 100-year range, or window. There are two types of windowing: fixed and sliding. The fixed method uses a fixed 100-year range. The sliding method uses a 100-year range that "slides" as the years progress over time.

Another web site at <a href="http://www.gensw.com/">http://www.gensw.com/</a> offers a possible solution. At this site is General Software, the maker of Embedded BIOS<sup>TM</sup> and Embedded DOS<sup>TM</sup>, providing pre-boot firmware adaptation kits for OEM developers of embedded computer systems. Their packages include source code, which means the BIOS code can be modified. The author has not investigated the feasibility of this embedded system package as a remediation solution to the TD anomaly, if such an anomaly exists.

If a TD anomaly shows up on a PC, and if the date/time has *advanced* into the future from the present time/date, it is proof positive that a TD anomaly has occurred. If the time/date has *retrogressed*, any number of causes applies, and it may *not* be a TD anomaly. This is explained further in this report.

Figure 1: How much luck do you need to hit the update period?

SCALE: 10 INCHES = 1 Second

SCALE: 1 INCH = 0.833 mSec or 100 FEET = 1 Second

### 5.0 Technical Dilation

### 5.1 Critical Treatise of Intel's Analysis of the Crouch-Echlin Effect Report

Mike Echlin submitted to Intel two sets of boards and a passive backplane for tests. This is Echlin's two sets of Zenith 286 12 MHz systems with a passive backplane. Each set consists of a CPU board with BIOS chips and an I/O board with an RTC chip. Each set is variously dubbed different names in Intel's report. See Intel Test Methodologies section in Intel's report for a list of equipment submitted to Intel by Mike Echlin.<sup>8</sup> In this report, these CPU boards are dubbed CPU #1 and CPU #2, as Intel does in most places in their report, although this naming convention is not consistent in their report.

Intel's report mentions Jace Crouch's "Zoom" 286-12 clone computer, which is the machine that first exhibited the TD anomaly in mid-1997 and started the whole series of investigations by individual researchers and companies. This anomaly was first reported by Mr. Jace Crouch on 27 August 1997 in the <a href="news:comp.software.year-2000">news:comp.software.year-2000</a> newsgroup. Intel's report also mentions Echlin's Gateway 486-33 computer. However, Intel has not examined either of these computers.

Intel's report also mentions a computer which was received by Compaq/Digital. <sup>10</sup> In further research, it turns out that this "machine" is a motherboard from the same Jace Crouch's "Zoom" 286-12 computer. <sup>11</sup> At Digital, the rest of a computer system was added to the motherboard, all of it new, including a new power supply. <sup>12</sup> According to Jace Crouch, the motherboard still exhibits the TD anomaly. <sup>13</sup>

This section is broken up into subsections below.

# 5.1.1 Award 4.50g Versus C&T SCAT BIOS

An excerpt from Intel's released public report states:

...The BIOS on this machine [Jace Crouch's affectionately called "Zoom" machine] is described as an Award 4.50g **and** a C&T SCAT BIOS on Echlin's website. These are not the same BIOS and we believe the C&T SCAT BIOS to be in error.<sup>14</sup> [Bold original]

According to Mr. Crouch's public rebuttal, the reverse is true. The AMI BIOS (*not* Award 4.50g BIOS) was first mentioned in an erroneous statement made by Mr. Crouch in a newsgroup message and subsequently the correction was made that the C&T SCAT BIOS was in fact the BIOS in use.<sup>15</sup> The author can vouch for the fact that this message was made long before Intel ever got involved in testing, or even heard of the concept of TD.

This message is shown on the next page. Note that there is not even a mention of an Award 4.50g BIOS. This message is the first of a series on public display on Mr. Jace Crouch's web site. <sup>16</sup>

Therefore, it follows that Intel didn't follow up on their "belief" by further research or by confirming with either Mr. Crouch or Mr. Echlin.

On page 14 of the report, a "C&T SCAT" computer is listed in the summary table of automated testing results. According to this table, this computer is a 386SX (Mr. Crouch's "Zoom" computer is a 286).<sup>17</sup>

Date: Wed, 27 Aug 1997 12:14:26 -0400 From: Jace <deleted> Newsgroups: comp.software.year-2000 Subject: y2k - strange results in DOS 6.22 On Wed, 27 Aug 1997, J. L. wrote: > I haven't done any WORK on the PC's SIMULATING Y2000 and beyond - because I > don't want my date and time stamps on some files messed up. But I'm > prepared to take a tape backup of my PC and then to run a proper Y2000 test > to see if anything freaky happens. I did this with one of the computers in my office: AMD 286-12, 8 megs RAM SCAT motherboard, AMI BIOS <NOTE: it is a C&T SCAT BIOS, I was mistaken when I wrote this. JC> 210M IDE hard drive New multi-I/O card w/ 2 fast serial ports MS-DOS 6.22 (no HD compression)

Don't laugh. It's still a screamer on Word Perfect 5.1, and with a SLIP connection is really fine for running a UNIX shell account! There are plenty of other boxes on campus that are even older; professors tend to keep their newer machines at home and use their old ones at the office.

Running a combination of DOS & win 3.1 apps

I did a backup, set the clock to 12-31-99, 11:55:00 and watched. The date rolled over to 00, and various WP and Microsoft applications showed a date of January 1, 2000. Files were saved to the HD with a year date of 00. The win 3.1 file manager read a year date of :0 on these files.

I let the system run for two weeks, and used it from time to time to make overheads, handouts, or handle e-mail. No files were uploaded or downloaded to our UNIX server, although I did keep using the SLIP connection to run Procomm as a terminal emulator. I'd leave the machine on all day, turn it off on nights and weekends. Normal stuff.

Here's what happened:

- 1. The system clock "ran" extremely rapidly. After two weeks, the system date was mid-December 2000. The date reported in CMOS and reported by various WP and Microsoft applications was identical. Whatever date the RTC reported, the applications displayed. Files were saved with a 00 year date, but win 3.1 file manager displayed a :0 date. These files were readable, writable, and seemed otherwise normal.

- 2. After about ten days, the system would not recognize that I had two serial ports. For whatever reason, every system test that I ran reported only one serial port. This was the case with Norton Utilities 7, MSD, and an old WP utility. Nothing else started shutting down, but I figured that if a serial port went down, anything could be next, maybe trash the hard drive in some strange time-warp way.

- 3. Once I set the system clock back to the correct 1997 date, both serial ports were recognized, and they worked fine. I have no idea why the clock "ran" so fast in y2k, nor why the system stopped recognizing the second serial port. This was enough to convince me that even on a simple PC, the y2k problem can cause hardware failures. Fortunately, I was running a word processor to prepare a few handouts and overheads for a history class, not administering the power grid for a three county area.

Peace & stocking up on sterno and propane and MRE's,

Jace

### Jace Crouch's Original Message (Bold Added)

### 5.1.2 Automated Cycling Test Results

In Appendix C of Intel's report, the summary table includes the two CPU boards submitted by Mike Echlin, but only one of the I/O boards was used for both CPU boards. This table is a summary of automated test data – in which power cycling was automated.

Presumably both I/O boards submitted by Mike Echlin have the same RTC chip, but there is no information other than the fact that the RTC chip is a Motorola part number MC146818 and is not buffered. The author has the same chip on several of his computers, including two 286 computers, but they are Hitachi chips (Japanese version). Both chips are exactly the same as the Motorola chip, as attested to by technical data on each. Yes, the author has the Hitachi data sheets dating back to 1987 – they were hard to find.

According to "Echlin System Test Methodology" section of Intel's report, during automated cycling tests Echlin's TDFIX utility was loaded on at least one of Echlin's CPU boards. The exact language of Intel's statement regarding the loading of TDFIX implies that this was done *during* the test. While this would invalidate the test results because any occurrence of the TD anomaly is circumvented by the TDFIX utility, it does not mean TDFIX was loaded in the *entire* test. Intel did try to "look for any unexpected jumps" in the system date/time. <sup>21</sup>

Intel states that they "...did not observe any case of the Crouch-Echlin Effect..." on either one of the two CPU boards. But this statement contradicts another statement: "TDFIX reported that it found the Crouch-Echlin Effect symptom... the utility is reporting discrepancies between RTC data and BIOS data, as on Mr. Echlin's Zenith." Another contradictory statement is: "On Processor Card #2, TDFIX.EXE was observed to intermittently detect a difference between the DOS system clock and the RTC...This discrepancy matched the value reported by TDFIX.EXE."

A discrepancy between RTC data and BIOS data, as explained in this report, is not necessarily a symptom of the TD anomaly. A time difference of only 2 seconds or so is not a valid symptom of a TD anomaly. But apparently Intel feels the need to report the findings of the TDFIX.EXE utility, yet without revealing the time difference. Evidence in textual analysis of their report indicates that Intel is attempting to show – without saying so – that the results of TDFIX utility is actually from the BIOS time conversion anomaly – which is true. But Intel is careful not to show the actual TDFIX time difference results.

Note that a *symptom* of the Crouch-Echlin Effect was observed, not the Crouch-Echin Effect itself. Nevertheless, Intel indicts itself by saying they "did not observe *any case* of the Crouch-Echlin Effect," which by definition should include any *symptom* of it.\*

But, as later shown in this report, the BIOS time conversion anomaly is not a case of the TD anomaly. Instead, a different time anomaly exists, and this is the ostensible reason the actual TDFIX time difference results are not revealed.

In April of 1999, a short series of newsgroup email messages ensued in a somewhat heated contention that the automated cycling test results is flawed because of the manner in which AC power to the test unit (a computer) is removed and then applied. There was even a claim that manually applying power to the test unit is somehow different from an automated power cycling method. From an engineering point of view, this is ludicrous. The method of power cycling makes no difference in the test results, especially since the power supply itself does not contribute to the anomaly.<sup>†</sup>

In the summary table in Appendix C, CPU #1 was power cycled 3108 times, CPU #2 was power cycled only 600 times, and the rest of the systems under the same test were power cycled 4026 times. No explanation was given for the apparent incompleteness of tests on CPU #1 and #2 boards.

# 5.1.3 Manual Cycling Test Results

In the Manual Cycling section of Appendix C, a two-page table of test data detailing manual cycling results appears. This test was conducted on Mr. Echlin's Zenith CPU board #2, which is the board that Intel stated exhibited "some anomalies with the BIOS".<sup>25</sup>

.

<sup>\*</sup> The counter-argument "That depends on what the definition of 'any case' is" is hardly valid, since the term "any case" makes the definition very broad.

<sup>†</sup> See Section 5.1, bottom half of 3<sup>rd</sup> paragraph.

The data shows that the test was begun on Wednesday, November 25, 1998, and ended on Wednesday, December 16, 1998, a period of 3 weeks. The data shows continuous daily entries from November 25 (Wed) to December 4 (Fri), which is a span of 10 consecutive days that includes the weekend of November 28 and 29. The recording stops on that Friday, December 4, resumes the following Monday, December 7, and continues to Tuesday, December 8. However, nothing is recorded on December 9, 10, and 11 (Wednesday through Friday inclusive). The recording resumes on Monday, December 14 and stops on Wednesday, December 16. A final recording is made on the first workday of the New Year (actual year 1999, computer year date 2001) on Monday, January 4, apparently to show the date after the rollover. 26

Intel's report states that an aggregated two-week test was performed, and this is attested to by the data in their report.<sup>27</sup> The system date was set to year 2000 during the test.

However, the other CPU board, CPU #1, was not tested using this methodology. Intel is not attempting to hide this fact. An excerpt reads in their report:

Intel has attempted to duplicate the Crouch-Echlin Effect on **one** of the systems that Mr. Echlin has observed to exhibit this anomaly. These are the steps we took to produce and analyze the Effect.<sup>28</sup>

[Bold added]

Based on Mr. Jace Crouch's public rebuttal statements on one of his pages, CPU board #1 is implied to be the board that has "exhibited TD very frequently," while CPU board #2 is implied to be the board that "may have exhibited TD on one occasion only." <sup>29</sup> This natural conjecture is based on Mr. Crouch's leading statement: "...guess which one [Intel] reported on?" (Intel reported on CPU board #2.) This is a leading statement that points the reader in the wrong direction: the presumption that CPU board #2 is the one that "may have exhibited TD on one occasion only," so that Intel is accused of testing the wrong board and ignoring the other board that has "exhibited TD very frequently." Compare this with Intel's own statement:

On CPU board #1 we did not observe any case of the Crouch-Echlin Effect, nor did TDFIX.EXE detect any discrepancy between the DOS system clock and the RTC. We also did not observe any case of the Crouch-Echlin Effect on CPU board #2; however, we did see some anomalies with the BIOS on this board. 30

[Bold added]

TDFIX did not find any problems with CPU board #1. And Intel makes a clarification regarding CPU board #2 in Appendix A of their report:\*

On Processor Card #2, **TDFIX.EXE** was observed to intermittently detect a difference between the DOS system clock and the RTC...This discrepancy matched the value reported by TDFIX.EXE. <sup>31</sup>

[Bold added]

Intel's statements show the *opposite* of Mr. Jace Crouch's veiled implication is true. CPU #1 is the board that "may have exhibited TD on one occasion only," and CPU #2 is the board that has "exhibited TD very frequently." The author's rendition of the truth is based on Intel's own statements regarding the reported *results of the TDFIX utility on each board*.†

Therefore, the CPU board tested in the manual cycling test is actually the board that exhibited the TD anomaly *frequently.*‡ And indeed the board does show evidence of the TD anomaly, and the proof is briefly shown here in this section and greatly expanded in Section 5.1.4.

A reader at CompuServe Year 2000 Forum reported that it is unclear whether Intel actually tested for the occurrence of TD *without* Mr. Echlin's TDFIX software installed. This is not true in the manual cycling test. An excerpt reads in Intel's report:

Mr. Echlin's machine was set up with only a PROMPT command in the AUTOEXEC.BAT and no CONFIG.SYS.<sup>32</sup>

The above excerpt stated that the AUTOEXEC.BAT file contains only a PROMPT command, and there was no CONFIG.SYS file. Hence, TDFIX was not loaded during manual cycling test.  $\S$

As a summary, Table 1 shows which board underwent which test, troubleshooting, or examination.

<sup>\*</sup> If you look carefully at these two excerpts, you will see a discrepancy in Intel's statements. This is already covered in Section 5.1.2 which see

<sup>†</sup> Also based on CPU #2 manual cycling test data and Appendix A, in which Intel commits a glaring blunder. See Section 5.1.4.

<sup>&</sup>lt;sup>‡</sup> This CPU #2 board, according to Intel, exhibited a BIOS INT 1Ah bug, and was cited in Intel's Appendix A.

<sup>§</sup> The author concedes it is possible to load TDFIX.EXE via AUTOEXEC.BAT, but has no reason to believe so based on careful analysis. The manual test data itself shows that the utility was not loaded: the test data shows evidence of a TD anomaly.

Note that the CPU #1 board was tested only in the automated cycling test. This board is the one that "may have exhibited TD on one occasion only." This board never did exhibit any TD anomaly through the TDFIX utility, according to Intel's statements. Since this board was tested in automated cycling test with TDFIX installed, the truth about this board will never be known, except for the statement Mr. Jace Crouch already made: that this board "may have exhibited TD on one occasion only," and the statement Intel already made: that TDFIX never found a problem with it. This author accepts at face value that CPU board #1 does <u>not</u> exhibit such an anomaly.

| Nomenclature                            | CPU #1     | CPU #2     |

|-----------------------------------------|------------|------------|

| Hypothesis #1 (Separate Code Paths)     |            | $\sqrt{}$  |

| Hypothesis #2 (Improper UIP Handling)   |            | $\sqrt{}$  |

| Hypothesis #3 (Interrupts Not Disabled) | $\sqrt{1}$ | √1         |

| Hypothesis #4 (DOS Kernel Time/Date)    | $\sqrt{1}$ | √1         |

| Hypothesis #5 (COMMAND.COM Conversion)  | Note 2     | Note 2     |

| Automated Cycling Test (Appendix C)     |            | $\sqrt{}$  |

| Manual Cycling Test (Appendix C)        |            | $\sqrt{}$  |

| Additional Observations (Appendix A)    |            | V          |

| BIOS INT 1A Handler Bug (Appendix E)    |            | $\sqrt{3}$ |

**TABLE 1: Board Test Summary**

### Notes:

1. Board numbers not mentioned in text

- 2. Board-independent test

- 3. Board number implied in Appendix A, page 12, next to last paragraph Appendix A is dedicated to CPU #2.

According to Hypothesis #2 section, Intel's investigation concludes the BIOS code on Echlin's 286 computer properly honors the UIP bit.<sup>33</sup> But Intel's statements indicate that the BIOS code was only cursorily examined, and no actual tests were performed to make or confirm this particular finding.\* In addition, it does not mention which board was examined, but the phrase "Echlin's boards" is mentioned in plural.

But regarding CPU board #2, a careful examination of the test data in Appendix C (pages 16-17) indeed shows some possible cases of the TD anomaly, all of them involving the time of day. But first, the caveats:

- 1. A wristwatch was used as a reference.

- 2. The accuracy of the wristwatch is not known but is a moot point since the seconds of time is not recorded.

\* However, extended analysis on the *characteristics* of the TD anomaly on Echlin's CPU #2 board shows indirect evidence that the UIP bit is being properly honored (see last parts of Section 5.1.4).

3. The wristwatch seconds of time is not included in the recorded reference time.

Notwithstanding the caveats, these cases show evidence of an advanced time relative to the reference time. An *advanced* time/date symptom is a strong indicator of the TD anomaly, as opposed to a retrogressed time/date symptom.

The time differences of these cases are shown in Table 2.† Since the time reference does not include the seconds of time, an accuracy of ±50 seconds is imposed before a case is considered evidence of an anomaly. This criteria permits a maximum reference time error of 16.7%. The differences are approximations only, rounded to the nearest half-minute. In the Delta column, a "+" indicates advanced time relative to the reference time, and a "-" indicates retrogressed time.

| Case | Day | Cycle | Delta (Secs) |

|------|-----|-------|--------------|

| 1    | 7   | 2     | +60          |

| 2    | 8   | 1     | +90          |

| 3    | 9   | 2     | +60          |

| 4    | 9   | 3     | +60          |

| 5    | 11  | 1     | +60          |

| 6    | 14  | 1     | +60          |

| 7    | 15  | 2     | +60          |

TABLE 2: Worst Case Evidence of TD Anomaly

An advanced time or date relative to the true time or date is proof positive that a TD anomaly is appearing. There is no scenario or condition identified with causing a false case of retrogressed time/date anomaly that <u>also</u> causes a false case of advanced time/date anomaly. In fact, there is no precedent for such an advanced time/date symptom.

Speaking of precedence, according to Mr. Michael Kennedy, the TD anomaly has been around since 1984, when the AT 286 computer was first introduced. According to Mr. Kennedy, the BIOS code listing released in 1984 shows it is not fully RTC-compliant.‡

<sup>&</sup>lt;sup>†</sup> The time differences are based on face value of the wristwatch reference time, with the seconds of time at 0 seconds.

<sup>&</sup>lt;sup>‡</sup> However, the BIOS code released the next year (1985) clearly shows the BIOS code has proper instructions to access the RTC date information, as well as the code for the time information. A masterful job was done in the source code, considering the limitations imposed by the hardware, the 286 processor chip included. The author has not seen the 1984 source code.

If the ±50 second criteria were changed to ±60 seconds, only Case 2 would qualify, and the maximum reference time error becomes a non-issue because the delta is greater than 60 seconds, which is the smallest resolution offered by a wristwatch without a second hand.

These cases should never occur on any computer just after a boot up. The maximum error to be expected on any boot up on any computer is about 2 seconds or so (on the retrogressed side, not on the advanced side).

There is but one flaw in this test methodology. A wristwatch is not in sync with the RTC, even if the RTC is set to the same time as the wristwatch. A better test is to examine the RTC, BIOS, and DOS time/dates just after computer boot by using the ViewCMOS program, written by Tom Becker. A typical TD anomaly would show a difference between the RTC and BIOS time/date information. The wristwatch test methodology will show this difference between the wristwatch and the reported DOS time, but will not reveal as much detail about the RTC, BIOS, and DOS.

It is already proven that the RTC is not the culprit for the TD anomaly in Section 5.3.3. Hence, examination of the RTC, BIOS, and DOS time/dates is much more appropriate and more accurate.

Using the ViewCMOS (or equivalent) program will easily determine whether a TD anomaly is being exhibited. A difference, especially a large one, between the RTC time/date information and DOS counterpart is evidence of a TD anomaly. If these are the same within 2 seconds or so, there is no TD anomaly, even if the RTC time/date does not show the correct time and date. In this case, the battery may be weak, or some other problem may be responsible. A number of causes applies to this symptom, but in no case should the RTC itself advance ahead in time. Again, this symptom is not a valid case of a TD anomaly.

Mr. Crouch once complained that Intel did not record the seconds of time on the wristwatch in their manual cycling test data. This missing portion of data is not lost; it is possible to reconstruct the wristwatch seconds of time based on Intel's own test data. This will be explained in no uncertain terms in the next section.

The issues herein will be addressed again and greatly expanded in the next section.

### 5.1.4 Glaring Intel Blunder

In Appendix A of Intel's report, an anomaly in the BIOS on Mr. Echlin's computer is reported and described.<sup>34</sup> In it, it is revealed that part of TDFIX function is to check the BIOS time (tick counts) against the RTC time. While it is prudent to cover this area of remediative fixes, it is nevertheless not the cause of the TD anomaly. It is merely a *symptom* of it; but caution must be voiced that a slight deviation of BIOS time from RTC time is quite normal and is not an indicator of a TD anomaly.\*

The RTC and BIOS time (tick counts) use different frequency sources, and they are not the same frequency. (Even if they were the same frequency, there would still be a drift between the RTC time and BIOS time, because they are not synchronized.†)

On computer startup, the time difference between RTC and BIOS/DOS is typically about 2 seconds, but as time goes on, the drift will widen slightly, depending on how long the computer remains powered on. However, a boot up will always "correct" or initialize the DOS time with the RTC time, since DOS time must be initialized with RTC time at every boot up.‡

Intel did not explain this. Neither, apparently, did Intel test their hypothetical analysis regarding boot ups at 47-minute (2820-second) intervals. They didn't do it because they knew they couldn't. This excerpt shows it is merely a theory:

**For example**, with Processor Card #2, if the computer was powered on at 12:47 AM the timer ticks in the BDA **would be** slow by 1 second; at 1:34 AM the timer ticks in the BDA **would be** slow by 2 seconds;...<sup>35</sup> [Bold added]

<sup>\*</sup> If a computer with a midnight rollover bug is left on over several days, there will naturally be a big difference between DOS date and RTC date. This is still not a valid indicator of a TD anomaly.

<sup>†</sup> That is, if *two* frequency sources were used at the same frequency. If a *single* frequency source were used for both RTC and BIOS/DOS, there would be no drift. Computer systems are not designed this way, because the RTC must have its own oscillator that continues to run with the computer powered off. This is why there is a slow drift of RTC time and BIOS time apart from each other the longer the computer remains powered on. Another reason is the oscillator is not oven-controlled, which means very slight variations of frequency due to ambient temperature changes inside the computer.

<sup>&</sup>lt;sup>‡</sup> Does not apply to operating systems that monitor the RTC directly instead of the BIOS for time/date information. These are: UNIX, OS/2, and Microsoft Windows NT.

This is a clever show of numbers without actually documenting the results from their own test data. Intel used a series of mathematical calculations based on the delta percentage of the two formulas shown in Appendix D (0.036%). These theoretical numbers are correct, as explained below.

Calculations based on this information shows that the time difference between each set of two example lines, except for two sets of them, is 2820 seconds, or exactly 47 minutes. The other two sets show a difference of 2760 seconds, or exactly 46 minutes. The 2820 figure roughly coincides with the 2809 seconds mentioned in Appendix D. Intel simply added 2820 seconds to the previous line to get the next time value, and increments the seconds in the phrase "will be slow by *n* seconds", where *n* is the incremented value. Only twice is the figure 2760 added instead of 2820.

But subterfuge is involved in the use of the 0.036% figure. Intel is laying blame on the Zenith BIOS conversion routine, but there is more to this and Intel's test data than meets the eye.

In Appendix D, two formulas are shown: one is a DOS algorithm (which is indeed undocumented); the other is a formula that Intel claims is used by the Zenith BIOS in Mr. Echlin's computer. The percentage figure noted (0.036%) is correct, the formulas will each result in a difference of 0.036 percent from the other. This difference is only relative to the DOS algorithm. Only the BIOS conversion routine is used during POST, not the DOS algorithm. The DOS algorithm is used for setting the time of day in the BDA (as well as in the RTC) by user interaction. The BIOS algorithm is used for setting the time of day in the BDA during POST. For Intel's purposes, the DOS algorithm is used only as a point of reference to show how far off the Zenith BIOS conversion routine really is. It has nothing to do with TD.

DOS uses another conversion routine (not the one highlighted in Appendix D) to convert from tick counts to a time format whenever the time needs to be displayed, or whenever a file needs to be time-stamped. An inaccurate tick count value in the BDA will be reflected in the time information returned by DOS.

The maximum error offset (introduced by the 0.036% offset from the true time) would be no more than 31 seconds, and this amount of offset would occur only if the Zenith 286 were booted at 23:59:59.\* This is hardly a case for a TD anomaly because the maximum error is only 31 seconds.

<sup>\*</sup> Ignoring, of course, the known midnight rollover bug.

Intel's calculations (shown on pages 11~12 of Intel's report) of the BDA tick counts using the 0.036 percentage figure is also correct, from a theoretical standpoint.

But Intel commits a glaring, pyrotechnical blunder in espousing the mathematical theory, because the theory *does not fit* the manual cycling test data results in Appendix C. The maximum offset error introduced by the 0.036% offset theory is *no more than 31 seconds*,† but the test data clearly shows some cases in which the time difference is *much more than 31 seconds*. The manual cycling test data in Appendix C and the theory expounded in Appendix A both refer to the same CPU board #2.

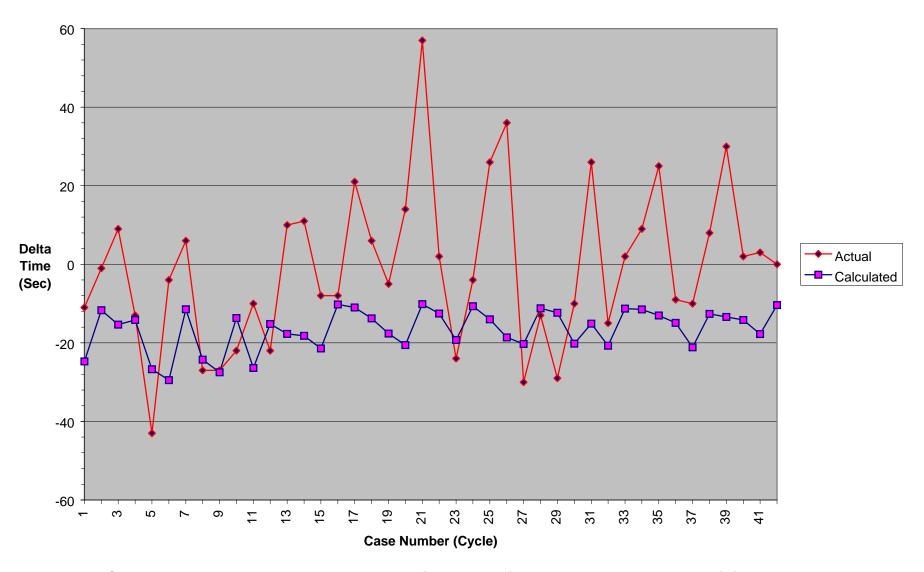

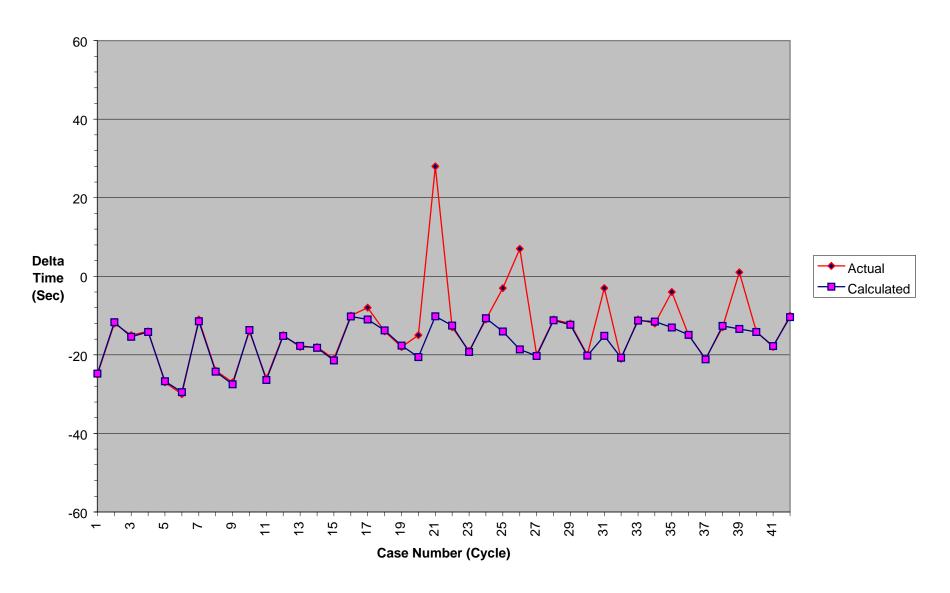

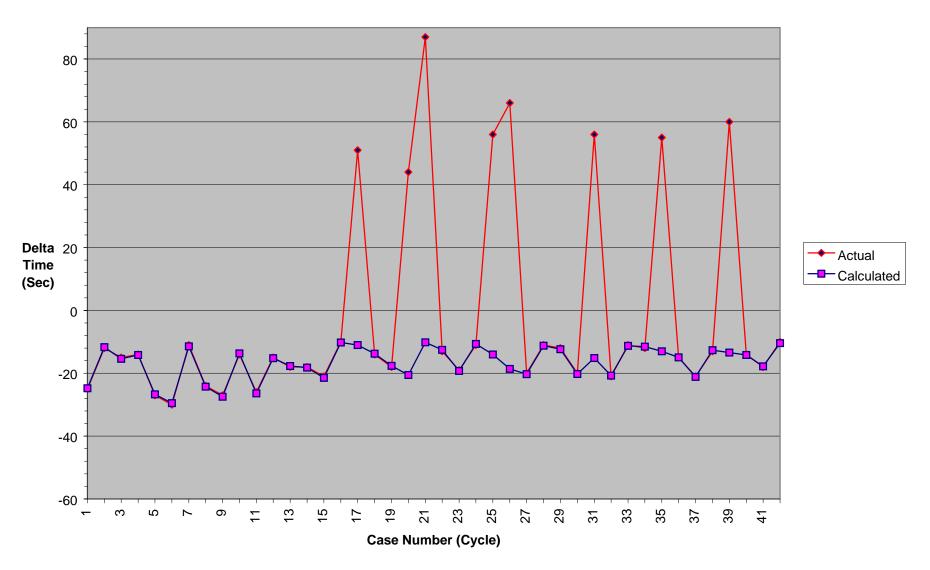

In Appendix A, the 0.036% offset theory reflects a *retrogressed* time anomaly ("the timer ticks in the BDA would be *slow* by..."). But some of the test data in Appendix C indicate an *advanced* time anomaly. Hence, the 0.036% offset theory and the test data do not fully support each other. This is graphically shown in Charts 2 and 3, but we are getting ahead of ourselves here.

### **Chart 1: Curious But Rough Pattern Match**

Intel's test data table does not include a column showing the time differences between the reference time (wristwatch) and the displayed time (DOS-reported time). These time differences are shown in Table 1 and Chart 1 at the end of this section. As already mentioned, the wristwatch reference time does not contain the seconds of time. For the purpose of this analysis, Chart 1 and Table 1 assume the reference time starts at 30 seconds. Thirty seconds is chosen because the error (or accuracy, depending on how one looks at it) in the reference time (wristwatch) is no more than +29/-30 seconds, since the minutes of time was recorded as part of the official data.

In Tables 1, 2, and 3, the Time Value columns contain decimal fractions ranging from 0 (zero) to 0.99999999, representing the times in the respective Date/Time columns from 00:00:00 (12:00:00 A.M.) to 23:59:59 (11:59:59 P.M.). The TIMEVALUE() function was used in Microsoft® Excel 97 to convert the time information in the Date/Time columns to decimal fractions in the respective Time Value columns.\*

\* These Time Value columns are not important for our consideration. More important are the Delta Time and 0.036% Ref Offset columns, as explained in the following text.

<sup>†</sup> If the Zenith 286 computer were booted at 23:59:59. If booted at an earlier time of the day, this error will be less than 31 seconds depending on the time of day. At midnight, the tick counts reset to zero and count upwards again. By Intel's definition, the amount of error offset is linearly proportional to the time of day.

Then the decimal fractions in the Wristwatch Time Value and Display Time Value columns are each converted into seconds, and the algebraic difference in seconds between them are shown in the Delta Time column. This data is plotted in Charts 1, 2, and 3 as a red line.

Finally, the Wristwatch Time Value data is first converted into seconds, then multiplied with 0.036% to compute the calculated (theoretical) offset in seconds that Intel claims would be reflected in the DOS-reported time. This computed offset is shown in the 0.036% Ref Offset column and is plotted in Charts 1, 2, and 3 as a dark blue line. All charts show the same plot as a reference plot, although the values in the 0.036% Ref Offset columns of Tables 1 and 2 are slightly different because the wristwatch seconds of time is mathematically adjusted in Table 2.

Note that the 0.036% Ref Offset data are all in negative values. The phrase "timer ticks in the BDA would be *SLOW* by..." reflects retrogressed time anomaly, hence the negative numbers. In other words, DOS-reported time is based on the tick counts in the BDA; theoretically speaking, if the tick counts is less than it should be, DOS reports a time that is less than it should be by the amount of time indicated in the 0.036% Ref Offset column.

The zero line in the charts represents zero deviation from the wristwatch reference time. A positive Delta Time value relative to zero is a case of an advanced time anomaly. A negative Delta Time value relative to zero is a case of a retrogressed time anomaly. Hence, the greater the time difference between the reference time (wristwatch) and DOS-reported time, the greater the deviation from the zero line.

A characteristic of a normal computer boot is that the DOS time is 2 seconds or so *behind* the RTC time. This is a normal case of "retrogressed" time. Thus a deviation of –2 seconds in the charts is a normal deviation. (Keep in mind, however, that the plotted deviation is based on a wristwatch, not the RTC time.) A deviation above –2 seconds (or perhaps –1 second in some computers) should never occur, and points to a unique anomaly because the DOS time (or date) theoretically should *never* be ahead of the RTC time (or date) when initialized in a computer boot.

Intel's test data contains a total of 42 boot cycles during the entire test period. The Case Number axis in the charts is the boot cycle number.

Red data points above the zero reference line are the cases in which the delta time is excessive compared to the zero reference line. Remember that the most deviation in time between the RTC and DOS on computer boot should be *no more than* –2 seconds or so. All these data points are strong cases for advanced time anomaly.

Case number 21 (Day 8, Cycle 1 in Intel's test data) is the strongest case for an advanced time anomaly, showing a delta of about 60 seconds from the zero reference time in Chart 1 (57 seconds in Table 1).

If all the wristwatch reference time data were changed to 0 (zero) seconds instead of 30 seconds in Chart 1 and Table 1, all data points in the plotted red line (actual) would be 30 seconds higher relative to the zero reference line than is shown in Chart 1. By the same token, a wristwatch reference time with 59 seconds of time would result in red data point values 29 seconds lower than is shown in Chart 1. The pattern of the plotted line itself will not change, as long as the wristwatch seconds of time in all Case Numbers are the same.

Therefore, Chart 1 only has a resolution of 59 seconds (+29/-30 seconds to be exact), because the wristwatch reference time in Intel's test data does not include the seconds of time. While Chart 1 does show proof that the actual results in Intel's test data does not match Intel's 0.036% offset theory in terms of peak-to-peak deviation,\* Chart 2 and 3 are more accurate and each solidifies this very proof. Chart 1 is based on a wristwatch reference time that includes exactly 30 seconds, as if the DOS-reported time was recorded when the reference time was exactly 30 seconds into the current minute of the wristwatch.

Chart 1 shows a very curious but very rough pattern match between the red line (actual) and the blue line (calculated). A study of the plotted lines in Chart 1 will bear this out. The "peaks" and "valleys" in both red and blue plotted lines roughly follow each other and the number of "peaks" and "valleys" are the same. This is borne out from the fact that the seconds of time in the Wristwatch Ref Time column are all the same, and the fact that the 0.036% offset error is *linearly proportional to the time of day*. This is the only characteristic that confirms Intel's reported Zenith BIOS 0.036% offset problem.

<sup>\*</sup> Peak-to-peak deviation: An engineering term defined as the delta between the two highest and lowest points in a plot.

#### **Chart 2: Best Case Scenario**

In order to positively confirm or deny the occurrence of the TD anomaly in Intel's test data, the seconds of time in the wristwatch reference time must be known. Hence, the author has attempted to reconstruct the actual seconds of wristwatch time during which the DOS-reported time and date was recorded. The result is Table 2 and Chart 2. How is this done? First, known factors must be established:

- 1. The wristwatch reference time in Intel's test data has a resolution of only 1 minute. Hence, only 59 seconds (+29/-30 seconds in Table 1) is allowed in the adjustment of the wristwatch reference time.

- 2. Intel's 0.036% offset theory is known and can be calculated based on Intel's own test data.